요약

본 기술은 MRAM의 각 메모리 셀을 2진 신경망의 가중치 저장을 위한 시냅스로 활용하여 2진 신경망에 대한 출력을 연산하는 새로운 아키텍처를 제시합니다. 이를 통해, 데이터 저장과 신경망의 출력 연산을 동시에 수행할 수 있어 효율성이 높아집니다. 또한, 이 기술은 AI 및 머신러닝 기반의 다양한 제품과 서비스 개발에 활용 가능하며, 기존 메모리 기반 아키텍처 대비 더 효율적인 신경망 연산이 가능하게 합니다.

기본 정보

•

특허명: 2진 신경망의 출력 연산을 위한 MRAM 기반의 연산 장치

•

대표 발명자: 나태희 교수

•

출원번호: 10-2023-0052465

발명의 배경 및 필요성

기술의 배경

•

최근 인공지능 기술에 대한 관심이 증가하면서 다양한 종류의 신경망 모델이 제시되고 있음

•

2진 신경망은 신경망의 가중치를 ‘+1’과’-1’의 이진 값으로 표현하여 구성한 신경망으로, 연산의 복잡도가 낮아 시스템 자원이 제한된 엣지 컴퓨팅 장치에서 주로 활용됨

•

최근에는 MTJ(Magnetic Tunnel Junction)를 저장소로 활용하는 MRAM이 등장하고 있으며, MRAM의 각 메모리 셀을 2진 신경망의 가중치 저장을 위한 시냅스로 활용하여 2진 신경망의 출력을 연산하는 아키텍처를 구성하는 방안이 고려되고 있음

•

2진 신경망에 대한 기계학습을 통해, 시냅스를 구성하는 각 가중치가 결정된 경우, 이 가중치를 MTJ의 저항 스위칭 특성을 이용하여 각 메모리 셀의 MTJ에 저장하고, 필요할 때 가중치를 읽어들여 2진 신경망에 대한 출력을 연산하는 MRAM 기반의 연산 아키텍처에 대한 도입이 고려되고 있음

기술의 필요성

•

2진 신경망은 XNOR(exclusive NOR) 동작을 지원해야 하기 때문에, 2진 신경망의 출력을 연산할 수 있도록 지원하는 새로운 아키텍처에 대한 연구가 필요함

•

본 발명은 MRAM의 각 메모리 셀을 2진 신경망의 가중치 저장을 위한 시냅스로 활용하여 2진 신경망에 대한 출력을 연산할 수 있는 새로운 아키텍처를 제시하고자 함

구현방법

기술의 원리

•

본 기술은 MTJ(Magnetic Tunnel Junction)의 특성을 활용함.

•

MTJ는 상단 전극에서 하단 전극으로 전류가 흐르면 낮은 저항을, 반대로 하단 전극에서 상단 전극으로 전류가 흐르면 높은 저항을 가짐.

•

전류의 방향을 조정함으로써 MTJ의 저항을 낮은 저항 또는 높은 저항으로 스위칭시킬 수 있어, 데이터를 저장하는 데에 사용될 수 있음.

구체적인 구현 방법

•

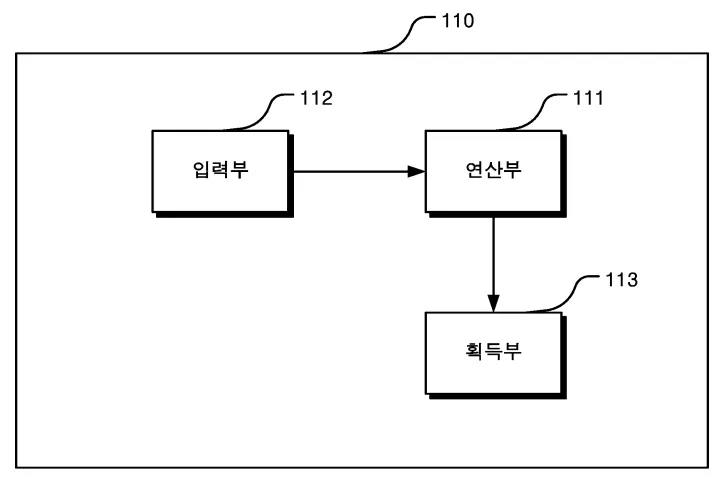

연산 장치는 연산부, 입력부, 획득부를 포함하며, 연산부는 하나의 트랜지스터와 하나의 MTJ로 구성된 메모리 셀들이 행과 열로 구성되는 어레이 구조로 배치됨.

•

입력부는 워드 라인을 통해 2진 신경망의 입력을 인가하며, 획득부는 각 열에 대응되는 카운터의 출력으로부터 2진 신경망의 출력을 획득함.

•

각 메모리 셀의 MTJ는 내부 저항 값이 제1 저항 값 또는 제2 저항 값 중 어느 한 저항 값으로 스위칭될 수 있는 소자로서, 이를 기반으로 2진 신경망에 대한 기계학습을 통해 지정된 ‘+1’ 또는 ’-1’이라는 이진 가중치를 저장하는 데에 사용됨.

기술의 장점

•

본 기술은 데이터 저장 및 2진 신경망의 출력 연산에 활용될 수 있음.

•

메모리 셀의 MTJ를 통해 이진 가중치 저장이 가능하며, 이를 통해 기계학습이 가능함.

•

데이터 저장과 신경망의 출력 연산을 동시에 수행할 수 있어 효율성이 높음.

실험 및 결과

실험의 목적

•

본 발명은 연산 장치의 구현과 이를 통한 2진 신경망의 출력 연산의 가능성을 확인하고자 함.

•

또한, 기계학습을 통해 이진 가중치를 저장하고, 이를 이용하여 신경망의 출력을 계산하는 과정을 검증하고자 함.

실험 방법 및 과정

•

n개의 성분들(In1, In2, In3, …, Inn)을, 상기 n개의 행들 각각에 하나씩 할당한 후, 상기 n개의 행들 각각의 워드 라인을 통해, 각 행이 할당된 성분에 대응되는 제어 전압을, 첫 번째 행부터 n번째 행까지 순차적으로 입력으로 인가함.

•

각 MTJ의 저항 값을 스위칭시키는 과정을 통해 이진 가중치를 저장하고, 이를 이용하여 신경망의 출력을 계산함.

•

각 열에 대응되는 감지 증폭기의 출력을 통해 신경망의 출력을 획득함.

실험 결과

•

연산 장치의 구현이 가능하며, 이를 통해 2진 신경망의 출력 연산이 가능함.

•

기계학습을 통해 이진 가중치를 저장하고, 이를 이용하여 신경망의 출력을 계산하는 과정이 정상적으로 작동함.

•

데이터 저장과 신경망의 출력 연산을 동시에 수행할 수 있어 효율성이 높음을 확인함.

발명의 활용 방안

제품 및 서비스에서의 적용

•

본 발명은 MRAM의 각 메모리 셀을 2진 신경망의 가중치 저장을 위한 시냅스로 활용할 수 있음

•

이를 통해, 2진 신경망에 대한 출력을 연산하는 새로운 아키텍처를 구현할 수 있음

•

AI 및 머신러닝 기반의 다양한 제품과 서비스 개발에 활용 가능함

산업 및 사회에서의 효과

•

기존 메모리 기반 아키텍처 대비 더 효율적인 신경망 연산이 가능함

•

해당 기술은 AI 및 머신러닝 산업의 성능 향상 및 효율성 증대에 기여할 것으로 예상됨

•

AI 및 머신러닝 기반의 제품과 서비스가 사회적 문제 해결에 더욱 효과적으로 활용될 수 있게 됨

기대효과

기술적 혁신

•

MRAM의 각 메모리 셀을 2진 신경망의 가중치 저장을 위한 시냅스로 활용하는 아키텍처는 기존 메모리 기반 아키텍처 대비 더 효율적인 신경망 연산을 가능하게 함

사회적 가치

•

본 발명을 활용한 AI 및 머신러닝 기반 제품과 서비스는 사회적 문제 해결에 더욱 효과적으로 활용될 수 있게 됨

•

또한, 이를 통해 AI 및 머신러닝 산업의 성능 향상 및 효율성 증대에 기여할 수 있음

장기적인 비전

•

본 발명이 일반화되면, AI 및 머신러닝 산업의 기술 발전과 성장에 크게 기여할 것으로 예상됨

기술 SWOT 분석

Strengths

효율적인 연산 가능

•

MRAM의 각 메모리 셀을 2진 신경망의 가중치 저장을 위한 시냅스로 활용하여, 기존 메모리 기반 아키텍처 대비 더 효율적인 신경망 연산이 가능합니다.

데이터 저장 및 신경망 출력 연산 동시 수행

•

메모리 셀의 MTJ를 통해 이진 가중치 저장이 가능하며, 이를 통해 기계학습이 가능합니다. 또한, 데이터 저장과 신경망의 출력 연산을 동시에 수행할 수 있어 효율성이 높습니다.

Weaknesses

기술적 복잡성

•

MTJ의 저항 값을 스위칭시키는 과정이 복잡하여, 이를 통해 이진 가중치를 저장하고 신경망의 출력을 계산하는 과정에 어려움이 있을 수 있습니다.

Opportunities

AI 및 머신러닝 기반 제품과 서비스 개발

•

본 기술은 AI 및 머신러닝 기반의 다양한 제품과 서비스 개발에 활용 가능합니다.

Threats

기존 메모리 기반 아키텍처와의 경쟁

•

기존에 널리 사용되고 있는 메모리 기반 아키텍처와의 경쟁에서 밀릴 수 있습니다.

시장 동향

인공지능 기술 및 시장 동향

MRAM 시장 동향

대표도면

인천대학교 산학협력단

(21999) 인천광역시 연수구 갯벌로 27(송도동) INU이노베이션센터 202호

본 메일은 마케팅 활용 동의서에 동의하신 회원님께 전송된 것입니다.

COPYRIGHT (c) 2023 Incheon National University. ALL RIGHT RESERVED.